DS04-23003-1E

# ASSP cmos 5V Single Power Supply Audio Interface Unit (AIU)

# MB86434

#### ■ DESCRIPTION

The FUJITSU MB86434 is an AIU (audio interface unit) LSI for +5 V single-power source digital telephone devices, manufactured using CMOS process technology. The codec transmission filter characteristics meet G.712 standards, and can handle input and output in A-Law,  $\mu$ -Law and linear conversion modes. The MB86434 also contains the necessary DTMF, microphone and receiver amps for telephone devices.

#### **■ FEATURES**

- +5 V single power supply

- Low power consumption: muting settings for each operating mode

Normal operation: 8.2 mA typ (speaker amp mute) Tone generation: 1.8 mA typ (speaker amp mute)

Standby mode : 0.5 µA typ

- On-chip codec filter meets G.712 standards

- Selection of codec conversion methods (A-law, μ-law, linear)

- On-chip low-noise microphone amp (2-channel) (unity gain frequency: 1MHz)

- On-chip receiver speaker amps (32 ΩBTL type: 10 mW MIN)

- On-chip tone speaker amp (32 ΩBTL type: 200 mW MIN)

- On-chip earphone speaker amps (32  $\Omega$  single type: 5 mW MIN)

(Continued)

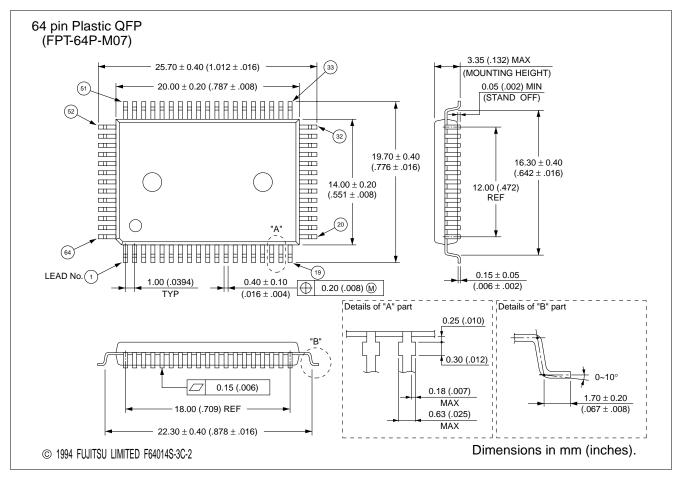

#### **■ PACKAGE**

64 pin, Plastic QFP

(FPT-64P-M07)

## (Continued)

- On-chip electronic volume gain adjustments (sending, receiving, tone)

- On-chip accessory output circuits

- DTMF generator function

- Service tone generation

- CMOS compatible input/output

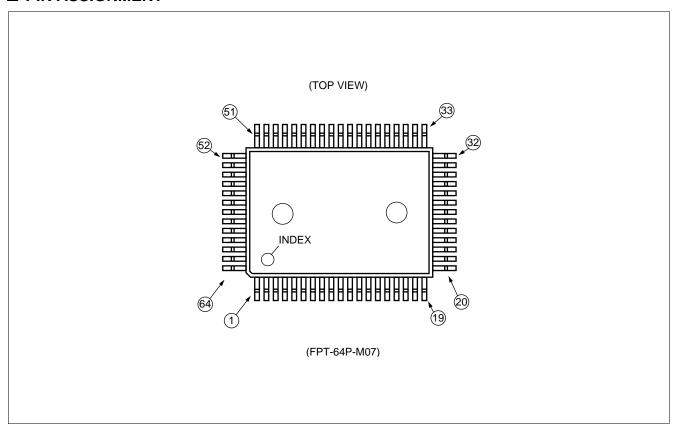

## **■ PIN ASSIGNMENT**

## **■ PIN DESCRIPTION**

| Pin No. | Symbol | I/O | A/D | Descr                                                                                                                                                                 | ription                                                                         |  |  |  |  |  |

|---------|--------|-----|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|--|--|--|--|--|

| 1       | CAG    | G   | Α   | Analog ground pin for codec block. To                                                                                                                                 | be set to 0 V.                                                                  |  |  |  |  |  |

| 2       | VRH    | 0   | Α   | Bypass capacitor connector pin for the circuit. Place capacitor between VRH                                                                                           | e A/D D/A reference voltage generator and CAG pins.                             |  |  |  |  |  |

| 3       | SGC    | 0   | Α   | Bypass capacitor connector pin for the circuit. Place capacitor between SGC                                                                                           |                                                                                 |  |  |  |  |  |

| 4       | VDDAC  | Р   | А   | Analog power supply pin for codec blo 5.25 V.                                                                                                                         | ock. To be set within range 4.75 to                                             |  |  |  |  |  |

| 5       | N.C.   | _   | _   | Not connected. To be left open.                                                                                                                                       |                                                                                 |  |  |  |  |  |

| 6       | N.C.   | _   | _   | Not connected. To be left open.                                                                                                                                       |                                                                                 |  |  |  |  |  |

| 7       | SYNC   | I   | D   | PCM codec send/receive synchroniza frequencies 8 kHz. CMOS interface. C block to power-down.                                                                          |                                                                                 |  |  |  |  |  |

| 8       | CLK    | I   | D   | Send/receive PCM signal series bit ra<br>law, A-law modes may be set to any le<br>and for linear in the range 256 k to 3.1<br>will cause part of codec block to power | evel in the range 64 k to 3.152 MHz,<br>152 MHz. Constant H or L level signal   |  |  |  |  |  |

| 9       | DIN    | I   | D   | PCM signal input pin. This signal is pic signal. CMOS interface.                                                                                                      | cked up internally at the fall of the CLK                                       |  |  |  |  |  |

| 10      | DOUT   | 0   | D   |                                                                                                                                                                       | in sync with the rise of the CLK signal. ization, and at power-down this signal |  |  |  |  |  |

| 11      | VDD    | Р   | D   | Digital power supply pin. To be set wit                                                                                                                               | hin range 4.75 to 5.25 V.                                                       |  |  |  |  |  |

| 12      | DG     | G   | D   | Digital ground pin. To be set to 0V.                                                                                                                                  |                                                                                 |  |  |  |  |  |

| 13      | PSC0   | I   | D   | Power-down control signal input pin. CMOS interface. Used with PSC1,2 pins for power-down settings.                                                                   | PSC 2 1 0<br>0 0 Full power-down                                                |  |  |  |  |  |

| 14      | PSC1   | I   | D   | Power-down control signal input pin. CMOS interface. Used with PSC0,2 pins for power-down settings.                                                                   | 1 0 0 V <sub>REF</sub> operating —1 0 Tone operating ——1 All operations         |  |  |  |  |  |

| 15      | PSC2   | I   | D   | Power-down control signal input pin. CMOS interface. Used with PSC0,1 pins for power-down settings.                                                                   | available<br>(—: value not determined)                                          |  |  |  |  |  |

| 16      | SRD    | I   | D   | 9-bit serial data input pin. CMOS interface. Data is written at the rise of the signal from this pin.                                                                 |                                                                                 |  |  |  |  |  |

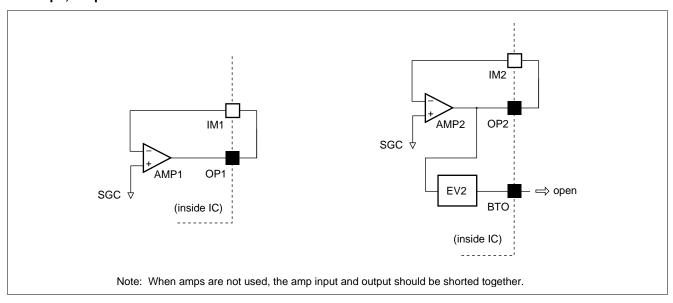

| 17      | SRC    | I   | D   | Clock input pin for 9-bit serial data wri at the rise of this pin.                                                                                                    | iting. CMOS interface. Data is written                                          |  |  |  |  |  |

| 18      | STB    | I   | D   | Serial data latch strobe signal. Data is interface. On-chip pull-down resistance                                                                                      |                                                                                 |  |  |  |  |  |

| 19      | XPRST  | I   | D   | Digital reset signal input pin. CMOS ir initialization H level: normal operation                                                                                      | nterface. L level: internal latch                                               |  |  |  |  |  |

| Pin No. | Symbol | I/O | A/D | Description                                                                                                                                                                     |

|---------|--------|-----|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

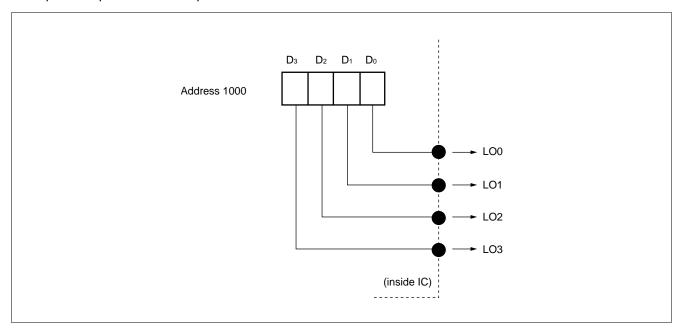

| 20      | LO0    | 0   | D   | External control latch output pin. Outputs value D <sub>0</sub> of address 1000. CMOS interface.                                                                                |

| 21      | LO1    | 0   | D   | External control latch output pin. Outputs value D <sub>1</sub> of address 1000. CMOS interface.                                                                                |

| 22      | LO2    | 0   | D   | External control latch output pin. Outputs value D <sub>2</sub> of address 1000. CMOS interface.                                                                                |

| 23      | LO3    | 0   | D   | External control latch output pin. Outputs value D <sub>3</sub> of address 1000. CMOS interface.                                                                                |

| 24      | TCLK   | I   | D   | Tone generator clock input pin. Can be used as a tone CLK signal by using address 1110 D4D3 to subdivide the internal clock signal by factors of 1/1, 1/2, 1/4. CMOS interface. |

| 25      | TONC   | I   | D   | Tone generator cycle control input pin. CMOS interface. Hlevel signal outputs tone.                                                                                             |

| 26      | LED    | 0   | D   | Ring LED control output pin. CMOS interface.                                                                                                                                    |

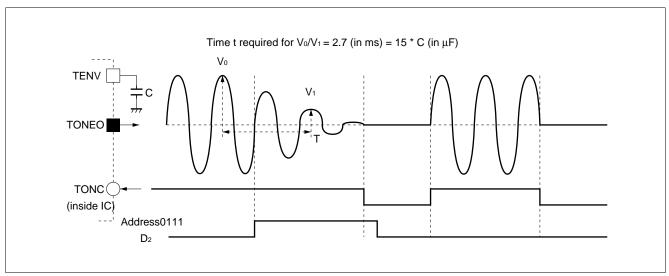

| 27      | TENV   | I   | Α   | Can be used to generate tone envelope, by placing capacitor between grounds and turning SW11 on/off.                                                                            |

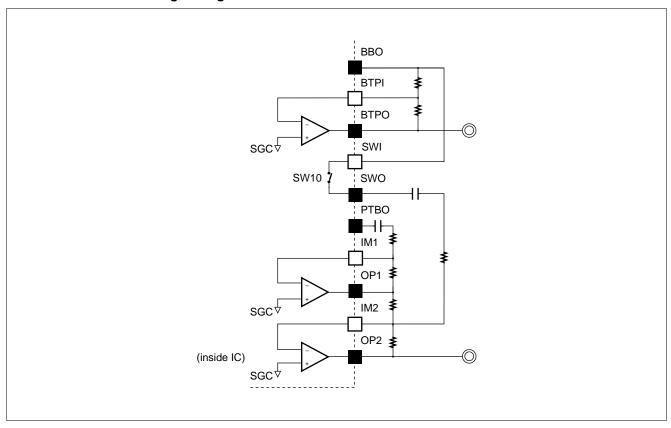

| 28      | SWO    | I/O | Α   | Analog switch 10 input/output pin. Controls address 0111 D <sub>0</sub> .                                                                                                       |

| 29      | SWI    | I/O | Α   | Analog switch 10 input/output pin.                                                                                                                                              |

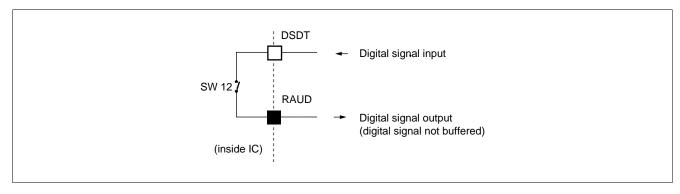

| 30      | DSDT   | I   | Α   | Accessory input. Can be connected to RAUD by switching paths.                                                                                                                   |

| 31      | TONEO  | 0   | Α   | Tone signal output pin.                                                                                                                                                         |

| 32      | RAUD   | 0   | А   | Output pin for external speaker, or audio test signal. Can be connected to DSDT by switching paths.                                                                             |

| 33      | VDDSP1 | Р   | Α   | Speaker amp power supply pin. To be set within range 4.75 to 5.25 V.                                                                                                            |

| 34      | JEAR   | 0   | Α   | Earphone speaker amp output pin. Capable of 5 mW output at 32 $\Omega$ load.                                                                                                    |

| 35      | XEAR   | 0   | Α   | Receiver speaker amp output pin. Internally connected to EAR and BTL. Maximum output of 10 mW can be obtained at 32 W load by connecting speaker between EAR and XEAR.          |

| 36      | EAR    | 0   | Α   | Receiver speaker amp output pin. Connected to XEAR and BTL.                                                                                                                     |

| 37      | SPG1   | G   | Α   | Speaker amp ground pin. To be set to 0 V.                                                                                                                                       |

| 38      | SPG2   | G   | Α   | Speaker amp ground pin. To be set to 0 V.                                                                                                                                       |

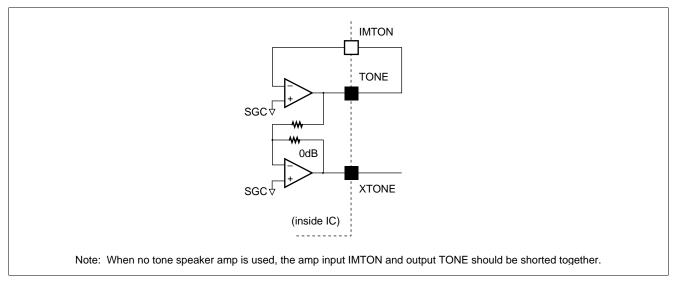

| 39      | XTONE  | 0   | Α   | Speaker amp tone output pin. Internally connected to TONE and BLT. Maximum output of 10 mW can be obtained at 32 $\Omega$ load by connecting speaker between TONE and XTONE.    |

| 40      | TONE   | 0   | A   | Speaker amp tone output pin. When speaker amp is not used for tone, TONE should be shorted to IMTON.                                                                            |

| 41      | IMTON  | I   | A   | Speaker drive inverted (–) signal input pin. Can be used to adjust gain by connecting resistance to TONE and IMTON.                                                             |

| 42      | VDDSP2 | Р   | Α   | Speaker amp power supply pin. To be set within range 4.75 to 5.25 V.                                                                                                            |

| Pin No. | Symbol | I/O | A/D | Description                                                                                                                                    |

|---------|--------|-----|-----|------------------------------------------------------------------------------------------------------------------------------------------------|

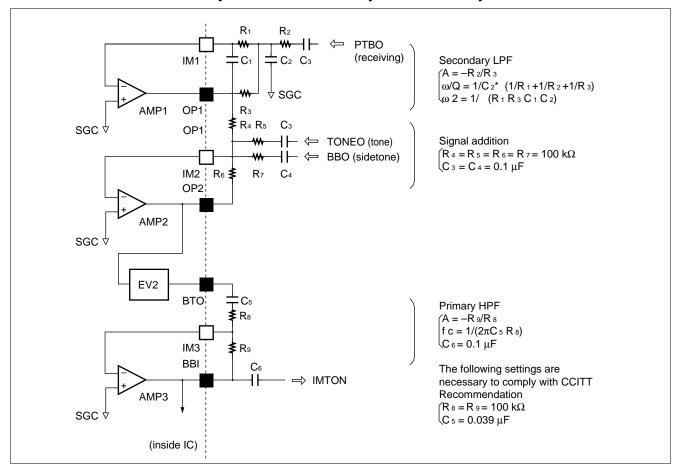

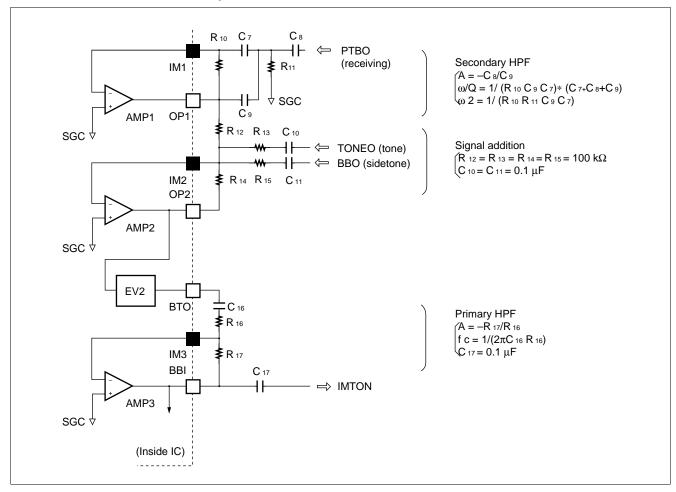

| 43      | BBI    | 0   | Α   | AMP3 output pin. Should be included in HPF together with IM3, to prevent DC offset from entering speakers.                                     |

| 44      | IM3    | I   | Α   | AMP3 inverted (–) signal input pin.                                                                                                            |

| 45      | вто    | 0   | Α   | Receiving volume adjustment circuit output pin.                                                                                                |

| 46      | OP2    | 0   | Α   | AMP2 output pin. If AMP2 is not used, IM2 should be shorted to OP2.                                                                            |

| 47      | IM2    | I   | Α   | AMP2 inverted (–) signal input pin. Can form a circuit with OP2 to add sidetone or tone. Melody circuits, if used, can also be connected here. |

| 48      | OP1    | 0   | Α   | AMP1 output pin. Can form a circuit with IM1 to include LPF or HPF in receiving block. If AMP1 is not used, IM1 should be shorted to OP1.      |

| 49      | IM1    | I   | Α   | AMP1 inverted (–) signal input pin.                                                                                                            |

| 50      | РТВО   | 0   | Α   | PCM receiver output pin.                                                                                                                       |

| 51      | BAG    | G   | Α   | Analog ground pin for sending, receiving blocks. To be set to 0 V.                                                                             |

| 52      | VDDAB  | Р   | Α   | Analog power supply pin for sending, receiving blocks. To be set within range 4.75 to 5.25 V.                                                  |

| 53      | XJMIC  | I   | Α   | Microphone amp (2) non-inverted (+) signal input pin.                                                                                          |

| 54      | JMIC   | I   | Α   | Microphone amp (2) inverted (–) signal input pin.                                                                                              |

| 55      | JMICO  | I   | Α   | Microphone amp (2) output pin.                                                                                                                 |

| 56      | XMIC   | I   | Α   | Microphone amp (1) non-inverted (+) signal input pin.                                                                                          |

| 57      | MIC    | I   | Α   | Microphone amp (1) inverted (–) signal input pin.                                                                                              |

| 58      | MICO   | 0   | Α   | Microphone amp (1) output pin.                                                                                                                 |

| 59      | SGO    | 0   | Α   | Sending block signal ground potential output pin. Buffers SGC voltage.                                                                         |

| 60      | вво    | 0   | Α   | Sending analog signal output pin.                                                                                                              |

| 61      | N.C.   | _   | _   | Not connected. To be left open.                                                                                                                |

| 62      | N.C.   | _   | _   | Not connected. To be left open.                                                                                                                |

| 63      | ВТРІ   | I   | Α   | PCM ENCODE block input OP amp negative input pin.                                                                                              |

| 64      | ВТРО   | 0   | Α   | PCM ENCODE block input OP amp output pin.                                                                                                      |

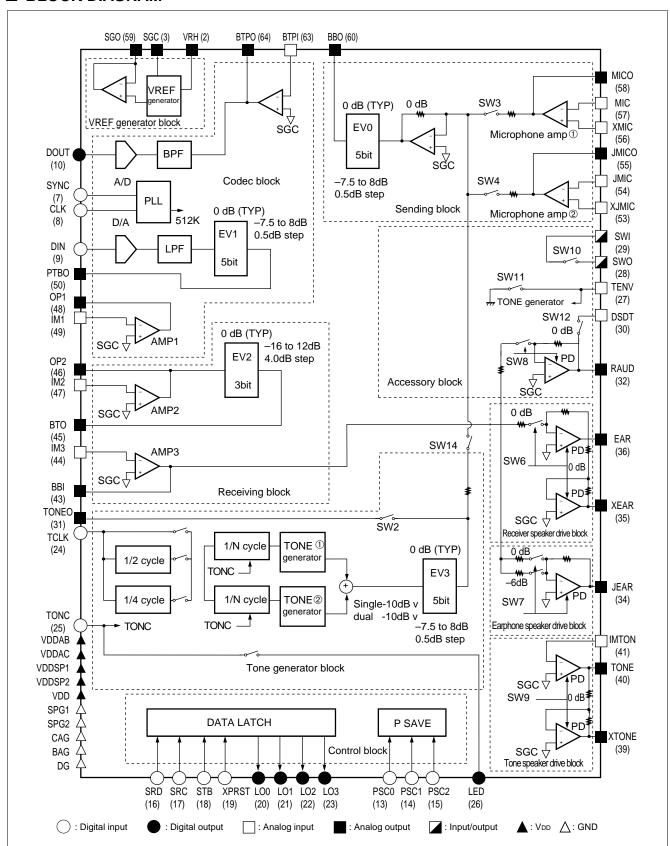

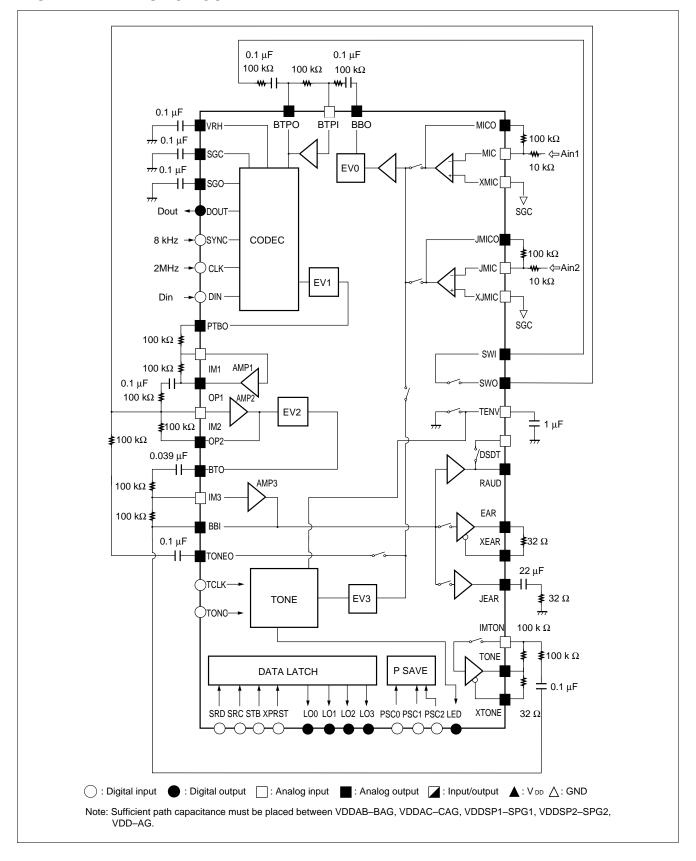

## **■ BLOCK DIAGRAM**

## **■ FUNCTIONAL DESCRIPTION**

## 1. Register Settings

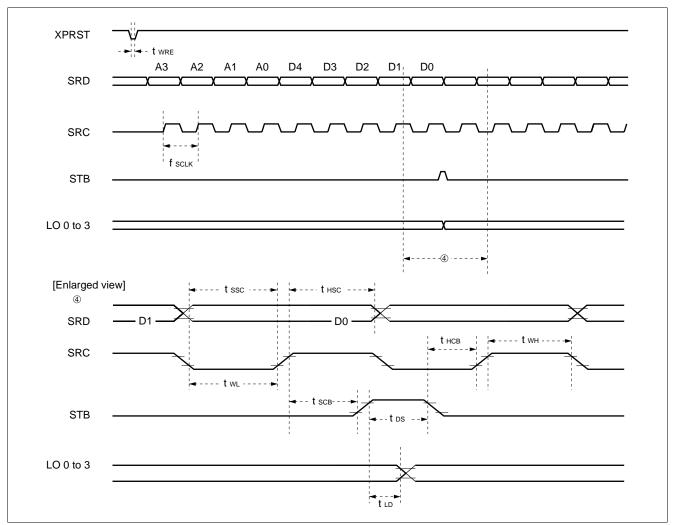

The MB86434 IC chip controls all electronic volume, switching, tone generator circuits and power-down control circuits by means of the SRD, STB and SRC data input signals.

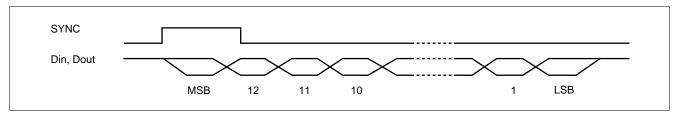

The MB86434 uses a 9-bit serial data format consisting of a 4-bit address followed by 5 data bits. Data is picked up at the rise of the SRC signal, and latched by the STB L-level signal. The 9-bits of serial data preceding the STB signal are considered valid. These register settings are not reset at power-down. They can be reset when data is initialized by an XPRST L-level signal.

## (1) Mode Settings

| Control | Address                                                     | Data bit                                                                   | Setting description                                                                    | Initial data bit setting (at reset)                                        | Remarks    |

|---------|-------------------------------------------------------------|----------------------------------------------------------------------------|----------------------------------------------------------------------------------------|----------------------------------------------------------------------------|------------|

| segment | A <sub>3</sub> A <sub>2</sub> A <sub>1</sub> A <sub>0</sub> | D <sub>4</sub> D <sub>3</sub> D <sub>2</sub> D <sub>1</sub> D <sub>0</sub> |                                                                                        | D <sub>4</sub> D <sub>3</sub> D <sub>2</sub> D <sub>1</sub> D <sub>0</sub> |            |

| EV0     | 0 0 0 1                                                     | D <sub>4</sub> D <sub>3</sub> D <sub>2</sub> D <sub>1</sub> D <sub>0</sub> | Sending audio level adjustment.<br>Adjusts EV0 gain.                                   | 0 1 1 1 1                                                                  |            |

| EV1     | 0 0 1 0                                                     | D <sub>4</sub> D <sub>3</sub> D <sub>2</sub> D <sub>1</sub> D <sub>0</sub> | Sending audio level adjustment.<br>Adjusts EV1 gain.                                   | 0 1 1 1 1                                                                  | *1         |

| EV2     | 0 0 1 1                                                     | * * D <sub>2</sub> D <sub>1</sub> D <sub>0</sub>                           | Sending audio level adjustment.<br>Adjusts EV2 gain.                                   | * * 1 0 0                                                                  |            |

| TX-MUTE | 0.4.0.0                                                     | D4 * * * D0                                                                | D <sub>0</sub> : Sending audio mute SW 3, 4 on/off control.  Mute: 1, Unmute: 0        | 0 * * * 0                                                                  | *2, *3     |

| RX-MUTE | 0 1 0 0                                                     | D <sub>4</sub> * * * D <sub>0</sub>                                        | D <sub>4</sub> : Receiving audio mute SW 6, 7, 8, 9 on/off control. Mute: 1, Unmute: 0 | 0 * * * 0                                                                  | *3, *4     |

| SW4     |                                                             |                                                                            | D <sub>1</sub> : JMIC mute SW 4 on/off control.<br>Mute: 1, Unmute: 0                  |                                                                            | *2         |

| SW3     | 0 1 0 1                                                     | D <sub>4</sub> * D <sub>2</sub> D <sub>1</sub> D <sub>0</sub>              | D <sub>2</sub> : MIC mute SW 3 on/off control.<br>Mute: 1, Unmute: 0                   | 0 * 0 0 0                                                                  | 2          |

| SW8     |                                                             |                                                                            | D <sub>4</sub> : RAUD mute SW 8 on/off control.<br>Mute: 1, Unmute: 0                  |                                                                            | *3, *4, *5 |

| SW6     |                                                             |                                                                            | D <sub>0</sub> : EAR, XEAR mute SW 6 on/off control. Mute: 1, Unmute: 0                |                                                                            |            |

| SW9     | 0 1 1 0                                                     | D <sub>4</sub> * D <sub>2</sub> D <sub>1</sub> D <sub>0</sub>              | D <sub>1</sub> : TONE, XTONE mute SW 9 on/off control. Mute: 1, Unmute: 0              | 0 * 0 0 0                                                                  | *4         |

| SW7     |                                                             |                                                                            | D <sub>2</sub> : JEAR mute SW 7 on/off control.<br>Mute: 1, Unmute: 0                  |                                                                            |            |

| ATT     |                                                             |                                                                            | D <sub>4</sub> : JEAR attenuation level switch. 0: 0.0 dB, 1: -6.0 dB.                 |                                                                            |            |

## (Continued)

|              | ontrol                     | Α          | dd             | res        | s  | Data bit                                                                   | Setting description                                                                                                                                                                              | _                |              | ata bit<br>t reset)                         | Remarks        |

|--------------|----------------------------|------------|----------------|------------|----|----------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|--------------|---------------------------------------------|----------------|

| se           | egment                     | <b>A</b> 3 | A <sub>2</sub> | <b>A</b> 1 | Αo | D <sub>4</sub> D <sub>3</sub> D <sub>2</sub> D <sub>1</sub> D <sub>0</sub> | gening accomplien                                                                                                                                                                                | D <sub>4</sub> D | 3 <b>D</b> 2 | <b>D</b> <sub>1</sub> <b>D</b> <sub>0</sub> | T.O.I.I.       |

| SW           | /10                        |            |                |            |    |                                                                            | D <sub>0</sub> : SWI-SWO switch SW 10 on/off control. On: 1, Off: 0                                                                                                                              |                  |              |                                             | *3, *6         |

| SW12         |                            |            |                |            |    |                                                                            | D <sub>1</sub> : DSDT pin selection SW 12 on/off control. On: 1, Off: 0                                                                                                                          |                  |              |                                             | *3, *5         |

| SW           | /11                        | 0          | 1              | 1          | 1  | D <sub>4</sub> D <sub>3</sub> D <sub>2</sub> D <sub>1</sub> D <sub>0</sub> | D <sub>2</sub> : Envelope generator<br>generate envelope (SW11 Off): 1<br>no envelope (SW11 On): 0                                                                                               | 0 (              | 0            | 0 0                                         | *3, *7         |

| SW           | /2                         |            |                |            |    |                                                                            | D <sub>3</sub> : TONEO mute SW 2 on/off control.<br>Mute: 1, Unmute: 0                                                                                                                           |                  |              |                                             | *8             |

| SW           |                            |            |                |            |    |                                                                            | D <sub>4</sub> : TONE sending add SW 14 on/off control. On: 1, Off: 0                                                                                                                            |                  |              |                                             |                |

| par          | rial/<br>rallel<br>nverter | 1          | 0              | 0          | 0  | * D <sub>3</sub> D <sub>2</sub> D <sub>1</sub> D <sub>0</sub>              | Parallel output $D_3 = LO3$ , $D_2 = LO2$ , $D_1 = LO1$ , $D_0 = LO0$                                                                                                                            | * (              | 0            | 0 0                                         | *9             |

| ΕV           | 3                          | 1          | 0              | 0          | 1  | D <sub>4</sub> D <sub>3</sub> D <sub>2</sub> D <sub>1</sub> D <sub>0</sub> | Tone level adjustment. Adjusts EV3 gain.                                                                                                                                                         | 0 1              | 1            | 1 1                                         | *1             |

|              |                            | 1          | 0              | 1          | 0  | X8 X7 X6 X5 X4                                                             | Tone (1) frequency control, set by 8-bit value $X_7$ to $X_0$ .                                                                                                                                  | 0 0              | 0            | 0 0                                         |                |

|              | Fre-                       | 1          | 0              | 1          | 1  | * X <sub>7</sub> X <sub>6</sub> X <sub>5</sub> X <sub>4</sub>              | $X_8 = 1$ to output trapezoidal wave, $X_8 = 0$ to output sine wave.                                                                                                                             | * (              | 0            | 1 0                                         | *40 *44        |

|              | quency<br>control          | 1          | 1              | 0          | 0  | Y <sub>8</sub> Y <sub>7</sub> Y <sub>6</sub> Y <sub>5</sub> Y <sub>4</sub> | Tone (2) frequency control, set by 8-bit                                                                                                                                                         | 0 0              | 0            | 0 0                                         | *10, *11       |

| <u>0</u>     |                            | 1          | 1              | 0          | 1  | * Y <sub>3</sub> Y <sub>2</sub> Y <sub>1</sub> Y <sub>0</sub>              | value $Y_7$ to $Y_0$ .<br>$Y_8 = 1$ to output trapezoidal wave, $Y_8 = 0$ to output sine wave.                                                                                                   | * (              | 0            | 1 0                                         |                |

| TONE control | Output                     |            |                |            |    |                                                                            | Tone generator control D <sub>0</sub> : tone (2) on/off control. On: 1, off: 0 D <sub>1</sub> : tone (1) on/off control. On: 1, off: 0 D <sub>2</sub> : LED output on/off control. On: 1, off: 0 |                  |              |                                             | *7, *8,<br>*12 |

| •            | Master<br>clock<br>control | 1          | 1              | 1          | 0  | D4 D3 D2 D1 D0                                                             | Tone CLK $D_4$ , $D_3$ 0 : FTCLK1/1 frequency selected 0 1 : FTCLK1/2 frequency selected 1 0 : FTCLK1/4 frequency selected 1 1 : Prohibited                                                      | 0 (              | ) 1          | 1 1                                         | *10            |

| РСМ          |                            |            | 1              |            |    | * * * D <sub>1</sub> D <sub>0</sub>                                        | PCM control D <sub>1</sub> , D <sub>0</sub> 0 0 : μ-law mode selected 1 0 : A-law mode selected 0 1 : linear mode selected                                                                       | * *              | . *          | 0 0                                         | *13, *14       |

| TE           | ST                         | 0          | 0              | 0          | 0  | D4 D3 D2 D1 D0                                                             | Do not write in test mode.                                                                                                                                                                       | 0 (              | 0            | 0 0                                         |                |

- \*1: See (4) Electronic Volume Controls

- \*2: See (2) Sending Audio Mute Setting

- \*3: See 5. Power Saving Modes

- \*4: See (3) Receiving Audio Mute Settings

- \*5: See 3. Analog Output (2) Accessory Output

- \*6: See 2. Analog Input (2) Accessory Input

- \*7: See (5) Tone Generator Circuit Tone Output Controls

- \*8: See (5) Tone Generator Circuit Tone Generator Control Output Level

- \*9: See (7) Parallel Output

- \*10: See (5) Tone Generator Circuit Tone Frequency Control Registers

- \*11: See (5) Tone Generator Circuit Tone Output Waveforms

- \*12: See (5) Tone Generator Circuit LED Output Controls

- \*13: See (6) Codec Input/Output

- \*14: See (7) The Codec SYNC Pin

## (2) Sending Audio Mute Settings

Switches SW 3 to SW 4 have the following functions. Address 0100 signals have priority.

|          |                |                | S              | etti           | ng             |                |                |                |                |                |          |           |         |

|----------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------|-----------|---------|

| Address  | <b>A</b> 3     | A <sub>2</sub> | Δ              | 1              | Ao             | Аз             | A <sub>2</sub> | Δ              | 1              | Ao             | Switchin | g setting | Remarks |

| Address  | 0              | 1              | (              | )              | 0              | 0              | 1              | (              | )              | 1              |          |           |         |

|          | D <sub>4</sub> | Дз             | D <sub>2</sub> | D <sub>1</sub> | D <sub>0</sub> | D <sub>4</sub> | Дз             | D <sub>2</sub> | D <sub>1</sub> | D <sub>0</sub> | SW3      | SW4       |         |

|          | _              | *              | *              | *              | 1              | _              | *              | _              | _              | *              | 0        | 0         |         |

| Data bit | _              | *              | *              | *              | 0              | _              | *              | _              | 1              | *              | _        | 0         |         |

| Data Dit | _              | *              | *              | *              | 0              | _              | *              | 1              | _              | *              | 0        | _         |         |

|          | _              | *              | *              | *              | 0              | _              | *              | _              | 0              | *              | _        | ×         |         |

|          | —              | *              | *              | *              | 0              | _              | *              | 0              | _              | *              | ×        | _         |         |

$\bigcirc$  : muted,  $\times$  : unmuted, — : not determined

## (3) Receiving Audio Mute Settings

Switches SW 6 to SW 9 have the following functions. Address 0100 signals have priority.

|          |                   |                       |                | S              | ettir          | ng             |                       |           |                       |                       |                  |                              |     |     |     |     |

|----------|-------------------|-----------------------|----------------|----------------|----------------|----------------|-----------------------|-----------|-----------------------|-----------------------|------------------|------------------------------|-----|-----|-----|-----|

| Address  | A <sub>3</sub> A  | <b>A</b> <sub>2</sub> | A <sub>1</sub> | A <sub>0</sub> | A <sub>3</sub> | A <sub>2</sub> | <b>A</b> <sub>1</sub> |           | <b>A</b> <sub>3</sub> | <b>A</b> <sub>2</sub> | g setting        |                              |     |     |     |     |

|          | D <sub>4</sub> D: | •                     |                |                | _              |                |                       | 1<br>1 Do | <b>0</b>              | D <sub>3</sub> [      | D <sub>2</sub> D | <b>0</b><br>1 D <sub>0</sub> | SW8 | SW7 | SW9 | SW6 |

|          | 1 *               | *                     | * *            | _              | _              | * _            |                       | _         | _                     | * -                   |                  | _                            | 0   | 0   | 0   | 0   |

|          | 0 *               | *                     | : *            | _              | _              | * _            |                       | _         | _                     | * -                   |                  | 1                            | _   | _   | _   | 0   |

|          | 0 *               | *                     | : *            | _              | _              | * _            |                       | _         | _                     | * _                   | _ 1              | _                            | _   | _   | 0   | _   |

| Data bit | 0 *               | *                     | . *            | _              | _              | * _            |                       | _         | _                     | *                     | 1 —              | _                            | _   | 0   | _   | _   |

| Data bit | 0 *               | . *                   | * *            | _              | 1              | * _            |                       | _         | _                     | * -                   |                  | _                            | 0   | _   | _   | _   |

|          | 0 *               | . *                   | * *            | _              | _              | * -            |                       | _         | _                     | * -                   |                  | 0                            | _   | _   | _   | ×   |

|          | 0 *               | . *                   | * *            | _              |                | * -            |                       | _         | _                     | * -                   | <b>–</b> 0       | _                            | _   | _   | ×   |     |

|          | 0 *               | *                     | * *            | _              | _              | * -            |                       | _         | _                     | *                     | 0 —              | _                            | _   | ×   | _   | _   |

|          | 0 *               | *                     | * *            | _              | 0              | * -            |                       | _         | _                     | * -                   |                  | _                            | ×   | _   | _   | _   |

$\bigcirc$  : muted,  $\times$  : unmuted, — : not determined

#### (4) Electronic Volume Controls

There are four different electronic volume controls, EV0 through EV3, with the following specifications. Electronic volume control settings are made by the SRD, SRC and STB signals, and setting values are reset by the XPRST signal. However, settings are not reset by PSC0, PSC1, PSC2 power-down mode operations.

Table 1 Relation of Volume Control Data bit Values to Gain

| Step                                                                                                                                                                               |                                                                                             | Data                                                                                             | bit v                                                                                                                                                                                                          | /alue                                                                                                                                                                                                                                                                                                                                                                                    | ė                                        | EV0<br>sending gain<br>adjustment                                                                                                      | EV1<br>receiving gain<br>adjustment                                                                                                                                                                   | EV2<br>receiver vol-<br>ume adjust-<br>ment | EV3<br>tone gain<br>adjustment                                                                                                         | Unit |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|------|

|                                                                                                                                                                                    | D <sub>4</sub>                                                                              | Дз                                                                                               | D <sub>2</sub>                                                                                                                                                                                                 | D <sub>1</sub>                                                                                                                                                                                                                                                                                                                                                                           | D <sub>0</sub>                           | Тур.                                                                                                                                   | Тур.                                                                                                                                                                                                  | Тур.                                        | Тур.                                                                                                                                   |      |

| 0<br>1<br>2<br>3<br>4<br>5<br>6<br>7<br>8<br>9<br>10<br>11<br>12<br>13<br>14<br>15<br>16<br>17<br>18<br>19<br>20<br>21<br>22<br>23<br>24<br>25<br>26<br>27<br>28<br>29<br>30<br>31 | 0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0 | 0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>0<br>0<br>0<br>0 | 0<br>0<br>0<br>0<br>1<br>1<br>1<br>1<br>0<br>0<br>0<br>0<br>0<br>1<br>1<br>1<br>1<br>1<br>0<br>0<br>0<br>0<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1 | 0<br>0<br>1<br>1<br>1<br>0<br>0<br>1<br>1<br>1<br>0<br>0<br>1<br>1<br>1<br>0<br>0<br>1<br>1<br>1<br>0<br>0<br>1<br>1<br>1<br>0<br>0<br>1<br>1<br>1<br>0<br>0<br>1<br>1<br>1<br>0<br>0<br>1<br>1<br>1<br>0<br>0<br>1<br>1<br>1<br>1<br>0<br>0<br>1<br>1<br>1<br>1<br>1<br>1<br>0<br>0<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1 | 0101010101010101010101010101010101010101 | -7.5 -7.0 -6.5 -6.0 -5.5 -5.0 -4.5 -4.0 -3.5 -3.0 -2.5 -2.0 -1.5 -1.0 -0.5 0.0 0.5 1.0 1.5 2.0 2.5 3.0 3.5 4.0 4.5 5.0 6.5 7.0 7.5 8.0 | -7.5<br>-7.0<br>-6.5<br>-6.0<br>-5.5<br>-4.0<br>-3.5<br>-2.5<br>-2.0<br>-1.5<br>-1.0<br>-0.5<br>0.0<br>1.5<br>2.0<br>2.5<br>3.0<br>3.5<br>4.0<br>4.5<br>5.0<br>6.5<br>7.0<br>6.5<br>7.0<br>7.5<br>8.0 | -16<br>-12<br>-8<br>-4<br>0<br>4<br>8<br>12 | -7.5 -7.0 -6.5 -6.0 -5.5 -5.0 -4.5 -4.0 -3.5 -3.0 -2.5 -2.0 -1.5 -1.0 -0.5 0.0 0.5 1.0 1.5 2.0 2.5 3.0 3.5 4.0 4.5 5.0 6.5 7.0 7.5 8.0 | dВ   |

Note: Each setting value is determined in relation to the initial setting value.

Returns to initial value at reset ( — parts)

EV2 data bits D<sub>4</sub>, D<sub>3</sub> are \*.

Table 2 Volume Gain Deviation

| Volume control No. | Condition                                                       | Min.                           | Тур.            | Max.                           | Unit |

|--------------------|-----------------------------------------------------------------|--------------------------------|-----------------|--------------------------------|------|

| EV0<br>EV1<br>EV3  | Gain deviation, with respect to reference value shown in Table1 | Reference<br>value<br>– 0.5 dB | Reference value | Reference<br>value<br>+ 0.5 dB | ٩D   |

| EV2                | Input frequency = 1020 Hz<br>Input level = - 20 dBv             | Reference<br>value<br>– 1.0 dB | Reference value | Reference<br>value<br>+ 1.0 dB | dB   |

## (5) Tone Generator Circuit

#### • Tone Frequency Control Registers

The tone generator uses a clock signal obtained by subdividing the TCLK clock signal input by 1/1, 1/2 or 1/4 according to the data bit in address 1110.

Table 3 Tone Clock Frequency Register Control

| Addres         | ss 1110               | Tone generator clock signal (f.,)         |

|----------------|-----------------------|-------------------------------------------|

| D <sub>4</sub> | <b>D</b> <sub>3</sub> | Tone generator clock signal (fin)         |

| 0              | 0                     | TCLK input clock signal                   |

| 0              | 1                     | TCLK input clock signal subdivided by 1/2 |

| 1              | 0                     | TCLK input clock signal subdivided by 1/4 |

| 1              | 1                     | Prohibited                                |

Frequency settings available through the tone frequency control register are determined by the following formula. Frequency setting  $f = f_{IN}/(12^*(1+n))$ , n = 1, 2, 3, ..., 255. (where  $f_{IN}$ : tone generator clock signal frequency). Therefore the available frequency setting range when  $f_{IN} = 512$  kHz is between  $f_{min} = 167$  Hz and  $f_{max} = 21333$  Hz.

Frequency settings corresponding to each DTMF rated reference frequency are shown in the following table.

Table 4 Tone Frequency Register Control

(Condition: 512 kHz)

|        |                        | Rated reference                       | Frequency |                |                                                                      | ddre<br>10/1 | - |                |                |          | ddre<br>11/11 |           |                |     | Error  |

|--------|------------------------|---------------------------------------|-----------|----------------|----------------------------------------------------------------------|--------------|---|----------------|----------------|----------|---------------|-----------|----------------|-----|--------|

| 1      | one type               | frequency<br>(generator<br>frequency) | setting   | D <sub>4</sub> | Data bit D <sub>4</sub> D <sub>3</sub> D <sub>2</sub> D <sub>1</sub> |              |   | D <sub>0</sub> | D <sub>4</sub> | Da<br>Da | ata k<br>D2   | oit<br>D₁ | D <sub>0</sub> | n   | EIIOI  |

|        |                        | 262 Hz                                | 261.7 Hz  | _              | 1                                                                    | 0            | 1 | 0              | *              | 0        | 0             | 1         | 0              | 162 | -0.11% |

|        |                        | 384 Hz                                | 384.4 Hz  | _              | 0                                                                    | 1            | 1 | 0              | *              | 1        | 1             | 1         | 0              | 110 | 0.10%  |

|        | vice tone<br>gle tone) | 400 Hz                                | 398.7 Hz  | _              | 0                                                                    | 1            | 1 | 0              | *              | 1        | 0             | 1         | 0              | 106 | -0.32% |

| (0     | 9.0 (01.0)             | 2000 Hz                               | 2031.7 Hz | _              | 0                                                                    | 0            | 0 | 1              | *              | 0        | 1             | 0         | 0              | 20  | 1.56%  |

|        |                        | 2600 Hz                               | 2666.7 Hz | _              | 0                                                                    | 0            | 0 | 0              | *              | 1        | 1             | 1         | 1              | 15  | 2.50%  |

|        |                        | 697 Hz                                | 699.4 Hz  | _              | 0                                                                    | 0            | 1 | 1              | *              | 1        | 1             | 0         | 0              | 60  | 0.34%  |

|        | Low tone               | 770 Hz                                | 775.7 Hz  | _              | 0                                                                    | 0            | 1 | 1              | *              | 0        | 1             | 1         | 0              | 54  | 0.74%  |

| _      | Low tone               | 852 Hz                                | 853.3 Hz  | _              | 0                                                                    | 0            | 1 | 1              | *              | 0        | 0             | 0         | 1              | 49  | 0.15%  |

| D<br>T |                        | 941 Hz                                | 948.1 Hz  | _              | 0                                                                    | 0            | 1 | 0              | *              | 1        | 1             | 0         | 0              | 44  | 0.75%  |

| M<br>F |                        | 1209 Hz                               | 1219.0 Hz | _              | 0                                                                    | 0            | 1 | 0              | *              | 0        | 0             | 1         | 0              | 34  | 0.82%  |

|        | Lligh tone             | 1336 Hz                               | 1333.3 Hz | _              | 0                                                                    | 0            | 0 | 1              | *              | 1        | 1             | 1         | 1              | 31  | -0.20% |

|        | High tone              | 1477 Hz                               | 1471.3 Hz | _              | 0                                                                    | 0            | 0 | 1              | *              | 1        | 1             | 0         | 0              | 28  | -0.38% |

|        |                        | 1633 Hz                               | 1641.0 Hz | _              | 0                                                                    | 0            | 0 | 1              | *              | 1        | 0             | 0         | 1              | 25  | 0.48%  |

Note: • Setting values are BIN display values

Error represents frequency setting error with respect to rated reference frequency.

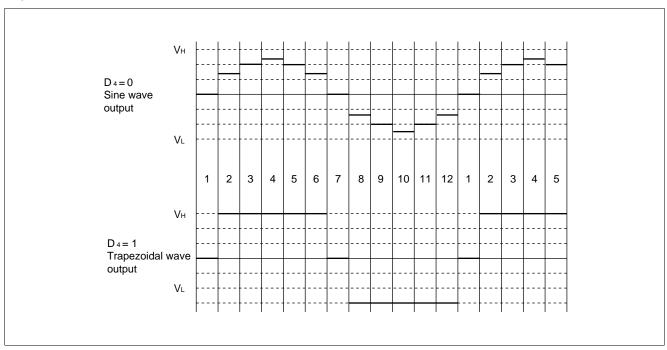

#### • Tone Output Waveform

The D<sub>4</sub> data bit at address 1010, 1100 may be used to select either sine-wave or trapezoidal waveforms for tone output.

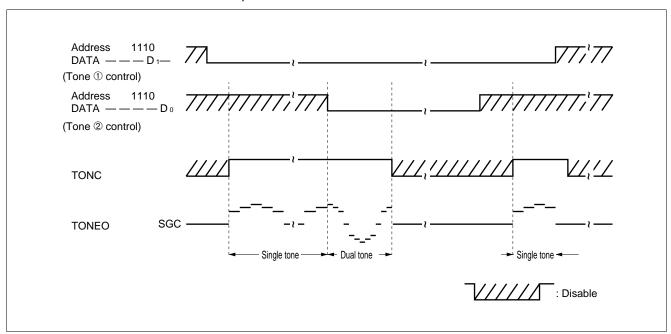

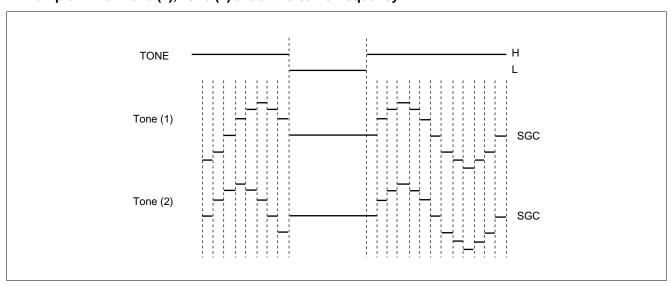

## • Tone Output Control

Tone output may be controlled by address and through the external tone control input pin TONC. In addition, the tone control offers a choice of sine or trapezoidal waveforms.

Also, by connecting a capacitor between the TENV pin and the ground, it is possible to generate an envelope for the tone waveform. Set address 0111 data bit  $D_2$  to 1 to generate. If an envelope is generated, silencing must be applied by an L-level signal from the TONC pin. The type of envelope that can be generated can be calculated approximately from the following formula.

## • LED Output Controls

Output from the LED output pins can be controlled by the TONC signal and the address 1110 data bit  $D_2$ . When the TONC signal is H-level, and the address 1110 data bit  $D_2$  value is L-level, the output level will be high. Output levels are CMOS levels.

## • Tone Generator Control Output Level

|      | al pins  |      | •    | ldre<br>111(<br>ta b | )              | Address<br>0111<br>data bits | circuit o            | enerator<br>perating<br>ode |             | ut pin<br>ode | Remarks |                    |

|------|----------|------|------|----------------------|----------------|------------------------------|----------------------|-----------------------------|-------------|---------------|---------|--------------------|

| PSC2 | PSC1     | PSC0 | TONC | D <sub>2</sub>       | D <sub>1</sub> | D <sub>0</sub>               | D <sub>3</sub> (SW2) | Tone<br>(1)                 | Tone<br>(2) | LED           | TONEO   |                    |

| 0    | 0        | 0    | _    | _                    | _              | _                            | _                    | ×                           | ×           | L             | H-Z     |                    |

| 1    | 0        | 0    | _    |                      |                |                              | _                    | ×                           | ×           | L             | H-Z     |                    |

| _    | 1 or 1   |      | 0    |                      | _              | _                            | 0                    | SGC                         | SGC         | L             | SGC     |                    |

| _    | 1 c      | or 1 | 0    | _                    | _              | _                            | 1                    | SGC                         | SGC         | L             | H-Z     |                    |

| _    | 1 c      | or 1 | 1    | 1                    | _              | _                            | _                    | _                           | _           | L             | _       |                    |

| _    | 1 c      | or 1 | 1    | 0                    | _              | _                            | _                    | _                           | _           | 0             | _       |                    |

| _    | 1 c      | or 1 | 1    | _                    | 1              | 1                            | 0                    | SGC                         | SGC         | _             | SGC     |                    |

| _    | 1 c      | or 1 | 1    | _                    | 1              | 0                            | 0                    | SGC                         | 0           | _             | -10 dBv | Single tone output |

| _    | - 1 or 1 |      | 1    | _                    | 0              | 1                            | 0                    | 0                           | SGC         | _             | -10 dBv | Single tone output |

|      | 1 or 1 1 |      |      | —                    | 0              | 0                            | 0                    | 0                           | 0           | _             | –10 dBv | Dual tone output   |

$\bigcirc$  : Operational,  $\times$  : Power down, H-Z : High-impedance, L: L-level fixed, SGC: SGC fixed

Note: When the TONC pin signal is L-level, the tone generator circuit counters will be reset. When a dual tone is generated at the time of reset, the initial phase settings for tone ① and tone ② will be in phase.

## • Example: When Tone (1), Tone (2) are at the same frequency:

## (6) Codec

## • Input/output

Both the  $\mu$ -law and A-law coding/decoding conversion processes used by the MB86434 codec are compatible with CCITT Recommendation G.711. In addition, linear coding in the form of 14-bit two's complement code can be output starting with MSB values.

| MSB Code LSB                            | PTBO reference voltage (V)                                 |

|-----------------------------------------|------------------------------------------------------------|

| 0 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 | 1.1766<br>to<br>2.3986<br>2.4000<br>2.4014<br>to<br>3.6235 |

#### • The codec SYNC pin

The codec block requires the input of an 8 kHz sampling clock signal at the SYNC pin, as well as a data transfer clock at the CLK pin. In order to conserve power consumption, whenever the SYNC pin or CLK pin signal is inactive, the system goes into SYNC power-down mode and stops code conversion.

Also, if either the SYNC or CLK pins encounters jitter of 5  $\mu s$  or greater, the system may go into power-down mode. Table shows the status of output pins in SYNC power-down mode.

| Pin symbol | Operation                |

|------------|--------------------------|

| SGC        | Normal operation (2.4 V) |

| SGO        | Normal operation (2.4 V) |

| VRH        | Normal operation (4.0 V) |

| DOUT       | H-level fixed            |

| PTBO       | SGC                      |

| ВТРО       | High impedance           |

## (7) Parallel Output

The LO0 to 3 pins carry latched output for external controls. The data written to address 1000 can be output through these pins. Output is CMOS output.

## 2. Analog Input

Analog input signals in the MB86434 include the two microphone inputs and the general-purpose analog switch.

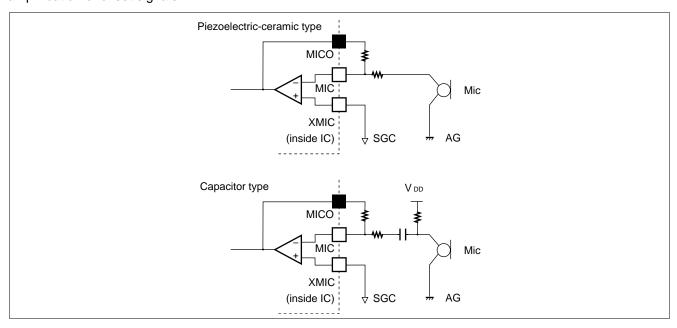

#### (1) Microphone Amps

The microphone amps take the incoming signal from the microphones and amplify it to any desired level of gain. The microphone lines are low-noise types for use with piezoelectric-ceramic or capacitor microphones, and are capable of a wide range of amplification. All microphones and amps must be coupled with capacitors to prevent amplification of offset signals.

| Parameter                                   | Characteristics (typ) |

|---------------------------------------------|-----------------------|

| Unity gain frequency                        | 1 MHz                 |

| Input conversion noise (BW = 300 - 3400 Hz) | 3.1 mV                |

| Maximum output level                        | 1.25 - 3.75 Vop       |

| Minimum load level                          | 50 kΩ                 |

## (2) Analog Switches

The analog switches include on-chip general-purpose switches with 1 k $\Omega$  in-resistance. Switches are controlled by writing to register address 0111 data bit D<sub>0</sub>, using H-level to make connections.

## • Sidetone addition using analog switches

## • SW10 = on

| Address                                                     | Data bit                                                                   |

|-------------------------------------------------------------|----------------------------------------------------------------------------|

| A <sub>3</sub> A <sub>2</sub> A <sub>1</sub> A <sub>0</sub> | D <sub>4</sub> D <sub>3</sub> D <sub>2</sub> D <sub>1</sub> D <sub>0</sub> |

| 0 1 1 1                                                     | 1                                                                          |

## 3. Analog Output

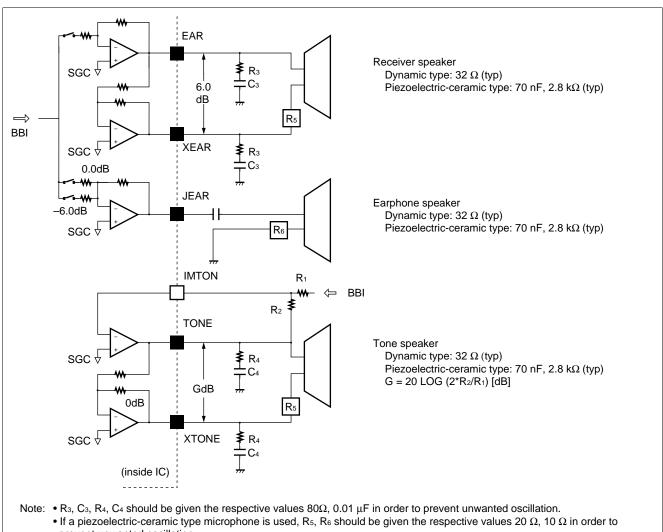

The MB86434 has a total of four analog output circuits, including the three speaker drive circuits (receiver, earphone and tone) and the accessory output.

## (1) Speaker Drive Amp

The speaker drive amps include two circuits (receiver and tone) with BTL output and one system (earphone) with single output. Because the speaker amp requires relatively high levels of power, it is connected to speaker selection switches (sw6-sw9) for power-down mode selection.

Two systems (receiver and earphone) have fixed gain levels, while the other system (tone) allows gain adjustment by means of external resistors.

In addition, the tone speaker amp is able to use the 200 mW large-current power circuit

Table Speaker Drive Amp Output Standards

| Parameter            | Receiver speaker amps (EAR, XEAR) | Earphone speaker amp (JEAR) | Tone speaker amps<br>(TONE, XTONE) |

|----------------------|-----------------------------------|-----------------------------|------------------------------------|

| Output type          | BTL                               | Single                      | BTL                                |

| Load resistance *1   | 32 Ω (typ)                        | 32 Ω (typ)                  | 32 Ω (typ)                         |

| Load resistance *2   | 2.8 kΩ (typ)                      | 2.8 kΩ (typ)                | 2.8 kW (typ)                       |

| Load capacity *2     | 70 nF                             | 70 nF                       | 70 nF                              |

| Final stage gain     | 6.0 dB                            | 0.0 dB/-6.0 dB              | -5 to 20 dB                        |

|                      | (between EAR-XEAR)                | (JEAR)                      | (between TONE-XTONE)               |

| Maximum output power | 10 mW (min)                       | 5 mW (min)                  | 200 mW (min)                       |

<sup>\*1:</sup> Dynamic-type speaker

<sup>\*2:</sup> Piezoelectric-ceramic type speaker

## **Analog Output Connection Example**

prevent unwanted oscillation.

## • Tone Speaker Amp Not Used

## (2) Accessory Output

The accessory output (RAUD pin) can carry either digital or analog output signals, and is controlled by address 0101 data bit  $D_4$  (SW 8), and address 0111 data bit  $D_1$  (SW 12).

When both SW 8 and SW 12 are in off position, the accessory outputline is in H-Z (high impedance) state. Caution: never place both SW 8 and SW 12 in on position at the same time. This may cause the MB86434 to function improperly.

#### • SW12 in On Position

| Address                                                     | Data bit                  |

|-------------------------------------------------------------|---------------------------|

| A <sub>4</sub> A <sub>3</sub> A <sub>2</sub> A <sub>1</sub> | $D_4  D_3  D_2  D_1  D_0$ |

| 0 1 1 1                                                     | 1 _                       |

#### • SW8 in On Position

| Address    |    |       |            |  | Data bit       |    |       |                |       |  |  |

|------------|----|-------|------------|--|----------------|----|-------|----------------|-------|--|--|

| <b>A</b> 4 | Аз | $A_2$ | <b>A</b> 1 |  | D <sub>4</sub> | Dз | $D_2$ | $\mathbf{D}_1$ | $D_0$ |  |  |

| 0          | 1  | 0     | 0          |  | 0              | *  | *     | *              | _     |  |  |

| 0          | 1  | 0     | 1          |  | 0              | *  | _     | _              | _     |  |  |

#### 4. Receiver Connections

It is possible to add tones and adjust sidetones by using amp 1,2 and 3 and the electronic volume control. When using amp 3, however, it is necessary to include HPF to avoid interference from the speaker amp DC.

• Tone and Sidetone Addition by Inclusion of Secondary LPF and Primary HPF.

#### · Amp1, Amp2 not used

## • Tone and Sidetone Addition by Inclusion of Third-Order HPF

## 5. Power Saving Modes

#### (1) Mode Selection

The MB86434 power saving modes can be controlled by using the external control signal lines (3 lines). It is also possible to apply power saving modes to the speaker amps with high power consumption levels by writing changes to register settings. Whenever the MB86434 changes directly from a power-down mode to normal operating mode, there is a possibility that speaker tones may be produced. The recommended sequence of coding changes to go into normal mode is (VREF mode)  $\rightarrow$  (Tone mode)  $\rightarrow$  (Normal mode).

#### **Power Saving Modes**

|                | _    |      | nal |     | d-    | Ad-   | Α     | ddre  |       |      | Output pin status |     |     |      |      |        |      |            |     | atiı | ng (     | circu    | it st | atus       |            |     |         |           |              |          |      |           |                 |

|----------------|------|------|-----|-----|-------|-------|-------|-------|-------|------|-------------------|-----|-----|------|------|--------|------|------------|-----|------|----------|----------|-------|------------|------------|-----|---------|-----------|--------------|----------|------|-----------|-----------------|

| Mode           | pins |      | dre | ess | dress |       | 0110  |       | A'R   | ٩ĸ   | 빌빌                | ď   | 5   | ပဝ   | 0.0  | စ္ကစ္စ | _    | BBO<br>VRH | _   | EC   | generato | generato | g     | ng         | ing        | one | ø       | sory      | Power supply |          |      |           |                 |

| WIOGE          | _    | _    | PS  |     | 04 D0 | 04 D0 | D4 D0 | D4 D0 | D     | D    | D                 | D   | EAR | JEAR | TONE | RAUD   | DOUT | 8GC<br>8GO | PP  | E E  | OP1      | B C      | BBI   | CODEC      |            | gen | Sending | Receiving | Receiving    | Earphone | Tone | Accessory | current<br>(mA) |

|                | C2   | . C1 | CO  | D4  |       |       |       |       | 04 D0 | 4 00 | יוטט              | SW8 | SW7 | SW9  | SW6  | SW6    | SW7  | SW9        | SW8 |      |          |          |       |            | MICO       |     |         | VREF      | TONE         | S        | _    |           |                 |

| All            |      |      |     |     |       |       |       |       |       |      |                   |     |     |      |      |        |      |            |     |      |          | >        | -     |            |            | 5W6 | 5W1     | 5009      | SW8          |          |      |           |                 |

| Power-<br>down | 0    | 0    | 0   | _   | _     | _     | _     | _     | _     | ZA   | H-Z               | ZB  | H-Z | Н    | H-Z  | ZC     | H-Z  | H-Z        | H-Z | *    | ×        | ×        | ×     | ×          | ×          | ×   | ×       | ×         | ×            | 0.0005   |      |           |                 |

| VREF           | 1    | 0    | 0   | _   | _     | _     | _     | _     | _     | ZA   | H-Z               | ZB  | H-Z | Н    | 0    | ZC     | H-Z  | H-Z        | H-Z | *    | ×        | 0        | ×     | ×          | ×          | ×   | ×       | X         | ×            | 0.48     |      |           |                 |

|                | _    | 1    | 0   | 1   | 1     | _     | _     | _     | _     | ZA   | H-Z               | ZB  | H-Z | Н    | 0    | 0      | H-Z  | H-Z        | H-Z | 0    | X        | 0        | 0     | ×          | 0          | X   | ×       | ×         | X            | 1.8      |      |           |                 |

|                | _    | 1    | 0   | 0   | 1     | 0     | 1     | 1     | 1     | ZA   | H-Z               | ZB  | 0   | Н    | 0    | 0      | H-Z  | H-Z        | H-Z | 0    | X        | 0        | 0     | ×          | 0          | X   | ×       | X         | 0            | 2.4      |      |           |                 |

| Tone           | _    | 1    | 0   | 0   | 1     | 1     | 0     | 1     | 1     | ZA   | 0                 | ZB  | H-Z | Н    | 0    | 0      | H-Z  | H-Z        | H-Z | 0    | X        | 0        | 0     | ×          | $\bigcirc$ | X   | 0       | ×         | ×            | 4.5      |      |           |                 |

|                | _    | 1    | 0   | 0   | 1     | 1     | 1     | 0     | 1     | ZA   | H-Z               | 0   | H-Z | Н    | 0    | 0      | H-Z  | H-Z        | H-Z | 0    | X        | 0        | 0     | ×          | 0          | X   | ×       | 0         | ×            | 6.8      |      |           |                 |

|                | _    | 1    | 0   | 0   | 1     | 1     | 1     | 1     | 0     | 0    | H-Z               | ZB  | H-Z | Н    | 0    | 0      | H-Z  | H-Z        | H-Z | 0    | X        | 0        | 0     | ×          | $\bigcirc$ | 0   | ×       | ×         | ×            | 6.8      |      |           |                 |

|                | -    | _    | 1   | 0   | 0     | 0     | 1     | 1     | 1     | ZA   | H-Z               | ZB  | 0   | 0    | 0    | 0      | 0    | 0          | 0   | 0    | 0        | 0        | 0     | 0          | 0          | ×   | ×       | ×         | 0            | 8.2      |      |           |                 |

|                | _    | _    | 1   | 0   | 0     | 1     | 0     | 1     | 1     | ZA   | 0                 | ZB  | H-Z | 0    | 0    | 0      | 0    | 0          | 0   | 0    | 0        | 0        | 0     | 0          | 0          | ×   | 0       | ×         | ×            | 10.3     |      |           |                 |

| Normal         | _    | _    | 1   | 0   | 0     | 1     | 1     | 0     | 1     | ZA   | H-Z               | 0   | H-Z | 0    | 0    | 0      | 0    | 0          | 0   | 0    | 0        | 0        | 0     | 0          | 0          | ×   | ×       | 0         | ×            | 12.6     |      |           |                 |

|                | _    |      | 1   | 0   | 0     | 1     | 1     | 1     | 0     | 0    | H-Z               | ZB  | H-Z | 0    | 0    | 0      | 0    | 0          | 0   | 0    | 0        | 0        | 0     | $\bigcirc$ | $\bigcirc$ | 0   | ×       | ×         | ×            | 12.6     |      |           |                 |

|                | _    |      | 1   | 0   | 0     | 0     | 0     | 0     | 0     | 0    | 0                 | 0   | 0   | 0    | 0    | 0      | 0    | 0          | 0   | 0    | 0        | 0        | 0     | $\bigcirc$ | $\circ$    | 0   | 0       | 0         | 0            | 20.9     |      |           |                 |

Note: • ○ : Operational, ×: Power-down, H-Z: High impedance, H: H-level fixed

: High impedance may not be applied, depending on status of SW6, SW7, SW8.

- ZA : EAR and XEAR are floating, however high resistance connection between EAR and XEAR.

- ZB: TONE and XTONE are floating, however, high resistance connection between TONE and XTONE, and between SGO and XTONE.

- ZC: Floating, however high resistance connection between OP2 and BTO. Codec in [Normal] mode operates with SYNC = 8 kHz, CLK = 2048 kHz.

- When RAUD is operating, address 0111 data bit D1 value should be "0" (SW12 off).

- In tone mode, address 0111 data bit D3 should be "0" (SW2 on), and address 0111 data bit D4 should be "0" (SW14 off).

- When the SYNC and CLK pin signals are fixed at either L-level or H-level, part of the codec unit will go into power-down mode. At this time the PTBO signal will be SGC level, BTPO will be H-Z, and VRH output will be approximately 4.0 V.

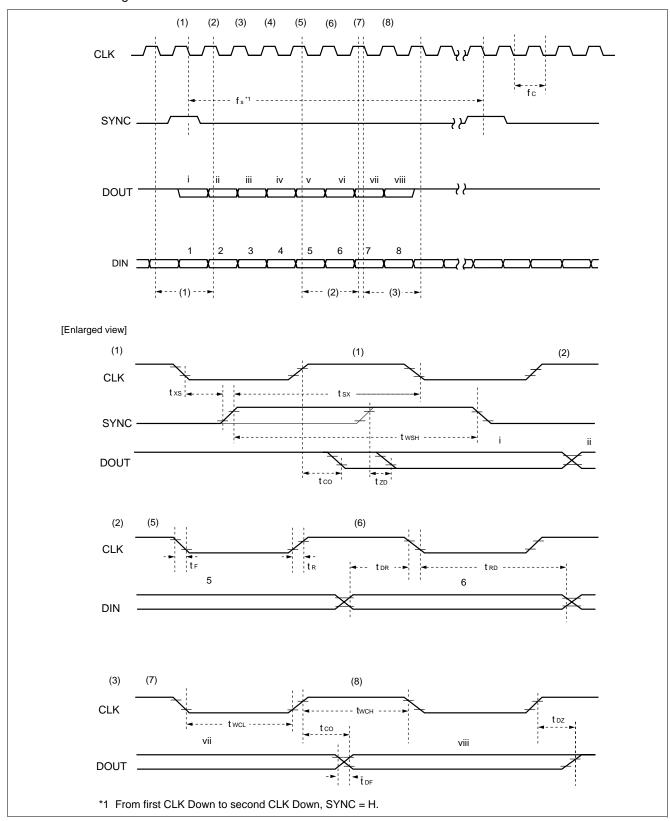

## **■ TIMING CHART**

• Codec-Related Signals

• Microcomputer Data-Related Signals

## ■ ABSOLUTE MAXIMUM RATINGS (See WARNING)

| Parameter             | Symbol | Ra   | Unit      |       |

|-----------------------|--------|------|-----------|-------|

| raiailletei           | Symbol | Min. | Max.      | Oilit |

| Power supply voltage  | Vs     | -0.3 | 7.0       | V     |

| Analog input voltage  | Vain   | -0.3 | +Vs + 0.3 | V     |

| Digital input voltage | Vdin   | -0.3 | +Vs + 0.3 | V     |

| Storage temperature   | Vstg   | -55  | +125      | °C    |

**WARNING:** Permanent device damage may occur if the above **Absolute Maximum Ratings** are exceeded. Functional operation should be restricted to the conditions as detailed in the operational sections of this data sheet. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## ■ RECOMMENDED OPERATING CONDITIONS

| Parameter                       | Symbol           | Pin name                              |      | Value |      |        |  |  |  |  |

|---------------------------------|------------------|---------------------------------------|------|-------|------|--------|--|--|--|--|

| Parameter                       | Symbol           | rin name                              | Min. | Тур.  | Max. | - Unit |  |  |  |  |

| Operating temperature           | Та               | _                                     | -20  | +25   | +80  | °C     |  |  |  |  |

| Power supply voltage            | Vs               | VDD, VDDAB, VDDAC,<br>VDDSP1 , VDDSP2 | 4.75 | 5.0   | 5.25 | V      |  |  |  |  |

| Digital input voltage           | VL               | All digital input pins                | 0.0  | _     | Vs   | V      |  |  |  |  |

| Analog output load resistance   | RLB              | BBO, PTBO, TONEO,                     | 75   | _     | _    | kΩ     |  |  |  |  |

| Analog output load capacity     | Сьв              | BTO, BTPO                             | _    | _     | 20   | pF     |  |  |  |  |

| Analog output load resistance*1 | RLE              | Between EAR-XEAR                      | _    | 32    | _    | Ω      |  |  |  |  |

| Analog output load capacity*2   | CLE              | Detween EAR-AEAR                      | _    | _     | 70   | nF     |  |  |  |  |

| Analog output load resistance*1 | RLJ              | JEAR                                  | _    | 32    | _    | Ω      |  |  |  |  |

| Analog output load capacity*2   | CLJ              | JEAR                                  | _    | _     | 70   | nF     |  |  |  |  |

| Analog output load resistance*1 | RLT              | Between TONE-XTONE                    | _    | 32    | _    | Ω      |  |  |  |  |

| Analog output load capacity*2   | Сьт              | Detween TONE-XTONE                    | _    | _     | 70   | nF     |  |  |  |  |

| Analog output load registeres   | R <sub>LM1</sub> | MICO, JMICO                           | 10   | _     | _    | kΩ     |  |  |  |  |

| Analog output load resistance   | R <sub>LM2</sub> | SGO, BBI, OP1, OP2                    | 50   | _     | _    | kΩ     |  |  |  |  |

| Analog output load capacity     | Сьм              | MICO, JMICO, SGO,<br>BBI, OP1, OP2    | _    | _     | 20   | pF     |  |  |  |  |

| Analog output load resistance*3 | RLM              | DALID                                 | 5    | _     | _    | kΩ     |  |  |  |  |

| Analog output load capacity*3   | Сьм              | RAUD                                  | _    | _     | 20   | pF     |  |  |  |  |

| Analog output voltage           | VAOUT            | All analog output pins                | 1.25 | _     | 3.75 | V      |  |  |  |  |

| Analog input voltage            | Vain             | All analog input pins                 | 1.25 | _     | 3.75 | V      |  |  |  |  |

<sup>\*1:</sup> Dynamic typ speakers

<sup>\*2:</sup> Piezoelectric type speakers

<sup>\*3:</sup> When SW8 = on, SW12 = off

## **■ ELECTRICAL CHARACTERISTICS**

## 1. DC Characteristics

|                                                                  |                                 | Coursels al | Di-                                           | O a malitia ma                                                                                               |        | Value |        | 11!4 |

|------------------------------------------------------------------|---------------------------------|-------------|-----------------------------------------------|--------------------------------------------------------------------------------------------------------------|--------|-------|--------|------|

|                                                                  | arameter                        | Symbol      | Pin                                           | Conditions                                                                                                   | Min.   | Тур.  | Max.   | Unit |

|                                                                  | ipply current at<br>r-down mode | Ivsst1      |                                               | PSC0 = 0 : PSC1 = 0 :<br>PSC2 = 0, Ain = AG,<br>Din = L                                                      | _      | 0.5   | 50     | μА   |

| Power su<br>VREF op                                              | upply current with perating     |             |                                               | PSC2 = 1, $Ain = SGC$ ,                                                                                      | _      | 480   | 800    | μА   |

| Power su<br>TONE of                                              | upply current with<br>perating  | Ivsst3      |                                               | PSC0 = 0 : PSC1 = 1,<br>Ain = SGC, Din = ICN<br>SW6 = SW7 = SW8 =<br>SW9 = off                               | _      | 1.8   | 3.0    | mA   |

| Power supply current for normal operation (only speaker ampmute) |                                 | Ivsst4      |                                               | PSC0 = 1, Ain = SGC,<br>Din = ICN<br>SW6 = SW7 = SW9 = off                                                   | _      | 8.2   | 12.0   | mA   |

| ` '                                                              | Receiver amps<br>EAR, XEAR      | IvssT5      | All V <sub>DD</sub> pins                      | PSC0 = 0, PSC1 = 1,<br>Ain = SGC, Din = ICN,<br>Power supply current<br>differential when SW6 is on/<br>off. | _      | 5.0   | 7.0    | mA   |